半導體行業深水區 聚焦集成電路設計領域的挑戰與破局之道

半導體行業作為現代科技的基石,其發展態勢深刻影響著全球產業鏈的格局。當前,行業雖歷經高速增長,但一系列深層次痛點依然存在,特別是在被譽為“芯片靈魂”的集成電路(IC)設計領域。這些挑戰既是攔路虎,也孕育著變革與躍遷的機遇。如何精準洞察痛點,并在此基礎上主動創造機會,是決定企業乃至國家在未來競爭中能否占據主動的關鍵。

一、 集成電路設計領域的主要痛點

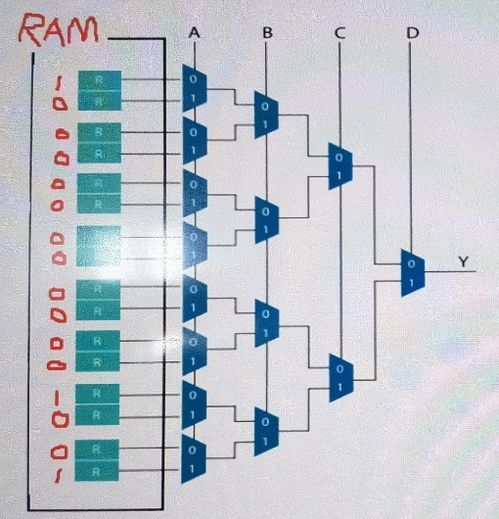

- 設計復雜度與成本飆升的“雙刃劍”:隨著工藝節點向5納米、3納米乃至更先進制程邁進,芯片集成度呈指數級增長。這意味著設計復雜度急劇升高,驗證工作量龐大,導致研發周期拉長,一次性工程費用(NRE)動輒高達數千萬甚至上億美元。高昂的成本和漫長的周期,使得中小設計企業難以涉足高端芯片研發,創新門檻被不斷推高。

- 人才短缺與結構性矛盾突出:IC設計是知識密集型產業,對高端人才依賴極強。全球范圍內,具備豐富經驗的架構師、資深設計工程師和驗證工程師嚴重短缺。人才培養周期長,高校教育與產業前沿需求存在一定脫節,形成了“需求旺盛”與“供給不足”并存的結構性矛盾,制約了行業整體創新能力的快速提升。

- 供應鏈安全與工具“卡脖子”風險:設計環節高度依賴EDA(電子設計自動化)軟件、IP核以及先進的晶圓制造能力。全球EDA市場由少數幾家巨頭壟斷,高端制造產能也集中在個別地區。這種依賴性在復雜國際環境下帶來了巨大的供應鏈不確定性,一旦受限,將直接導致設計活動停擺。

- 應用場景碎片化與定制化需求:在人工智能、物聯網、汽車電子等新興領域,應用場景高度細分,對芯片的性能、功耗、成本提出了多樣化且嚴苛的定制要求。傳統通用型芯片難以完美滿足,而針對每個場景進行全流程定制設計,又將面臨上述成本與周期壓力。

二、 于變局中開新局:創造機會的路徑探索

面對上述痛點,消極回避只會固守困境,主動創新方能化挑戰為機遇。集成電路設計領域的破局之道,可從以下幾個維度展開:

- 擁抱設計方法學與工具創新,降低復雜度門檻:

- 大力發展國產EDA與先進IP:這是解決供應鏈安全與成本問題的根本。通過政策扶持與市場驅動,集中攻堅全流程EDA工具,并構建自主可控、豐富多樣的高質量IP核庫,降低設計基礎工具的使用門檻和成本。

- 推廣基于先進封裝和Chiplet的設計理念:不必盲目追逐最尖端工藝。通過將大型單片系統分解為多個功能明確的芯粒(Chiplet),采用先進封裝技術進行集成,可以復用成熟工藝模塊,顯著降低單芯片設計復雜度、制造成本和研發風險,實現性能與成本的平衡。

- 深化人工智能與機器學習在EDA中的應用:利用AI技術輔助進行架構探索、布局布線、驗證測試等,可以大幅提升設計自動化水平,縮短周期,優化芯片PPA(性能、功耗、面積)。

- 構建多元化人才生態與協同創新模式:

- 產學研用深度融合:鼓勵企業與高校、科研院所共建聯合實驗室、定制化人才培養項目,讓課程設置與項目實踐緊跟產業需求,加速培養即戰型人才。

- 開源硬件與開放生態建設:借鑒RISC-V開源指令集架構的成功經驗,積極參與和推動設計生態的開放。降低芯片架構的入門壁壘,吸引全球開發者貢獻創意,形成繁榮的社區和創新土壤,分散對封閉生態的依賴。

- 聚焦垂直領域,深耕場景化與平臺化設計:

- 從“通用”轉向“場景定義”:深入理解自動駕駛、數據中心、智能穿戴等垂直行業的特定需求,提供“芯片+算法+軟件”的一體化場景解決方案,而非單純的硬件。通過深度定制創造更高附加值。

- 打造可重構與平臺化芯片:設計具備一定靈活性和可配置性的硬件平臺(如FPGA與ASIC結合,或可編程加速器),使其能夠通過軟件調整來適應一定范圍內變化的應用需求,以平臺的彈性應對市場的碎片化。

- 強化產業鏈協同與生態合作:

- 設計-制造-封裝協同優化:加強IC設計公司與晶圓廠、封裝廠的早期合作,開展設計工藝協同優化,從設計端就考慮制造可行性和成本,提升整體效率。

- 構建應用驅動的創新聯盟:聯合終端設備廠商、軟件開發商、系統集成商,形成以最終應用為導向的產業聯盟,共同定義芯片規格,共享市場與風險,加速創新落地。

###

半導體行業的痛點,尤其是集成電路設計環節的挑戰,是產業邁向更高階段必須跨越的關隘。它迫使從業者不能止步于跟隨,而必須轉向原始創新與生態構建。機會永遠垂青于前瞻布局和主動變革者。通過聚焦方法學革新、人才戰略、垂直深耕與生態協同,集成電路設計完全有能力將當下的壓力轉化為未來發展的強大動力,在半導體行業的深水區中,開辟出新的航道,驅動整個產業行穩致遠。

如若轉載,請注明出處:http://www.wopou.cn/product/23.html

更新時間:2026-03-27 18:49:22